DRAM: ¿Qué es?, ¿Cómo Funciona?, y sus Tipos

La DRAM (Dynamic Random-Access Memory) es un tipo de memoria de acceso aleatorio (RAM) que utiliza un condensador y un transistor como método de almacenamientos de bits de datos; dicho condensador suele perder la carga cada cierto tiempo, por lo tanto, se necesita de un sistema de refresco que lea y rescriba los datos frecuentemente.

Diccionario de la DRAM

- Celda de memoria: La celda de memoria es un circuito electrónico donde se guarda un bit de información binaria, esta información es importante, ya que depende de esta comunicar si la celda de memoria está cargada o no.

- Matriz: Dentro de las memorias DRAM, una matriz es la forma ordenar los millones y millones de celdas de memoria, es decir, mediante la matriz, se simplifica lo que es la dirección de un dato.

- Bancos de memoria: Los bancos de memorias cumplen la función de guardar una matriz, comúnmente dentro de un chip puede haber hasta 8 de estos, aunque este número puede cambiar.

¿Cómo Funciona la DRAM?

Estructura de las Celdas de una DRAM

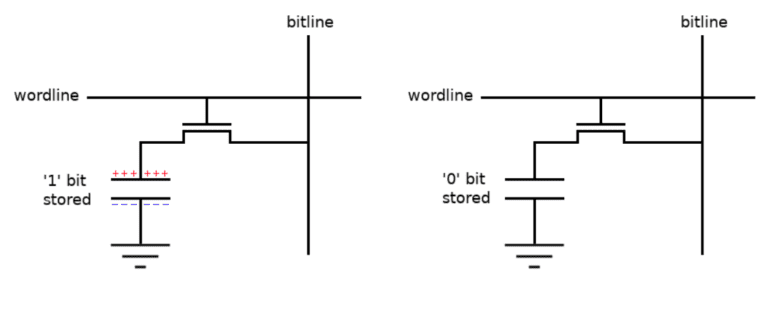

Para entender el funcionamiento de la DRAM es necesario entender que las celdas de almacenamiento se componen de dos partes: un condensador y un transistor.

La función de estos elementos es sencilla, el condensador se ocupa de almacenar las cargas enviadas con un valor lógico alto (es decir “1”), no obstante, si el condensador no está almacenando alguna carga, el valor lógico es bajo (es decir “0”). En el caso del transistor, este funciona como un interruptor para la carga/descarga del condensador.

Dentro de la celda de memoria, la carga/descarga se realiza mediante la “wordline” y la “bitline”, dichas líneas trabajan junto al transistor, por lo tanto, durante una lectura/escritura la “Worldline” funciona como una señal para el transistor para conectar la “bitline” con el condensador, esto con el fin de cargarlo, para descargar el condensador la “Worldline” envía una señal al transistor para dejar salir la energía, todo este sistema se encarga de almacenar un bit de almacenamiento.

No obstante, para almacenar un software no es suficiente, teniendo en cuenta que cada celda de almacenamiento solo puede contener un bit, pues, se necesitarían 8.000.000 de celdas para almacenar un único Megabyte, por lo tanto, para ejecutar un software serían necesarios millones y millones de celdas.

¿Cómo se organiza?

Todas las celdas se encuentran dispersas a través de los distintos bancos de memoria de la DRAM, dentro de estos bancos se encuentra una matriz, esto con el fin de organizar las celdas y simplificar las direcciones de cada bit de dato mediante sensores.

Nota: La matriz está formada de filas y columnas, siendo las filas las Worldlines y las columnas las bitlines

¿Cómo se leen los datos en una Memoria DRAM?

La carga almacenada en cada celda es demasiado pequeña como para ser notada por un sensor, por lo tanto, cada señal emitida por una celda pasa a través de un amplificador de detección que determina si el valor lógico es alto o bajo (es decir, si es “1” o “0”), esta información es retransmitida con un mayor voltaje mediante la columna de la matriz (bitline), para finalmente ser leída por el sensor correspondiente.

Nota: Al detectar un valor lógico alto (es decir “1”), el amplificador de detección se encarga de devolver el valor lógico a la celda con el fin de guardar el valor.

¿Cómo se escriben los datos en una Memoria DRAM?

Todo el proceso anterior es con el fin de leer los datos almacenados en la DRAM, en cambio, para escribir datos el proceso es algo más sencillo, dentro de la matriz se activan filas (wordlines) y la energía entra a través de las columnas (bitlines) con el fin de llenar con una carga eléctrica el condensador ubicado en cada celda.

Nota: Al escribir dentro de la DRAM es sin distinción, es decir, la carga eléctrica accederá a cada celda este o no cargada, esto debido a que las columnas y filas se conectan con cada celda al mismo tiempo.

DRAM Asíncrona

La DRAM Asíncrona (Asynchronous Dynamic Random Access Memory) es el primer tipo de memoria DRAM utilizado, se le llama “asíncrona” debido a que el acceso a la memoria no está coordinado con el reloj del sistema/CPU; este tipo de memorias solo se encuentran en los computadores más antiguos, por lo que su fabricación es muy inusual.

FPM RAM (Fast Page Mode RAM)

FPM RAM es una tipo de modificación a la primera generación de memoria DRAM Asíncrona, esta fue desarrollada con el objetivo de mejorar el rendimiento de lecturas y escrituras mediante un soporte de direcciones abreviadas, es decir, si la siguiente celda a leer/escribir se ubica en la misma línea que la anterior, su ubicación se determina únicamente por el número de columnas.

La FPM RAM apareció en 1990 con un ancho de bus de 64 bits y una velocidad de reloj/transferencia de 25 MHz, no obstante, esta sería remplazada en 1995 por la EDO DRAM.

EDO DRAM (Extended data out DRAM)

EDO DRAM es la versión definitiva de las memorias DRAM asíncronas, este tipo de memoria fue desarrollado con el objetivo de mejorar el rendimiento del estándar de los 90s (FPM RAM).

Además de tener las características de su antecesor (FPM RAM), añadió la capacidad de eliminar los tiempos de espera entre ciclos, teniendo la capacidad de seleccionar una nueva columna mientras se leen los datos de la columna anterior, dicha capacidad haría que el rendimiento aumentara hasta en un 30% en comparación con su antecesor (FPM RAM).

La EDO DRAM se inventó en 1990 y apareció en 1994 con un ancho de bus de 64 bits y una velocidad de reloj/transferencia de 40 MHz, no obstante, esta seria remplazada en 1996 por la SDR SDRAM.

SDRAM

Las SDRAM (synchronous dynamic random-Access memory) es una serie de memorias DRAM cuyas operaciones (lectura, escritura, actualización, etc.) está sincronizado con el reloj del sistema/procesador.

SDR SDRAM

SDR SDRAM (Single Data Rate Synchronous Dynamic Random-Access Memory) es un tipo de memoria de la serie SDRAM que está diseñada solo para leer o escribir un ciclo de datos del reloj.

SDR SDRAM (Single Data Rate Synchronous Dynamic Random-Access Memory) es un tipo de memoria SDRAM que está diseñada para leer/escribir datos una sola vez por ciclo de reloj. Este tipo de memoria eran muy comunes en los años 90s, frecuentemente siendo muy utilizado en Procesadores de la época (AMD K6, AMD Athlon K7, Pentium II, etc.)

En 1996 las memorias SDR SDRAM remplazo a su antecesor asíncrono (EDO DRAM), este tipo de memorias contaba con diversos tamaños de buses (4, 8, 16, etc.) y con una velocidad de reloj/transferencia que iban desde 66 MHz hasta 200 MHz.

Nota: SDR SDRAM es normalmente abreviado como “SDRAM”, obviamente, esto esta mal, pero la cultura del internet es muy xd.

DDR SDRAM

DDR (Double Data Rate) es un tipo de memoria SDRAM que tiene como característica principal el realizar dos operaciones de lectura/escritura por cada ciclo de reloj, a diferencia de su antecesor (SDR SDRAM) que solo podía realizar una operación de lectura/escritura por ciclo de reloj.

Una de las características de este tipo de memorias es que ninguna generación (versión) es compatible entre sí.

Otro detalle a destacar, es que, con la llegada de dicha tecnología se comenzó a popularizar el concepto “MT/s” como remplaza de los MHz, esto debido a que los MT/s es una medida más exacta para las memorias DDR, no obstante, el término MHz sigue siendo usado por temas de marketing.

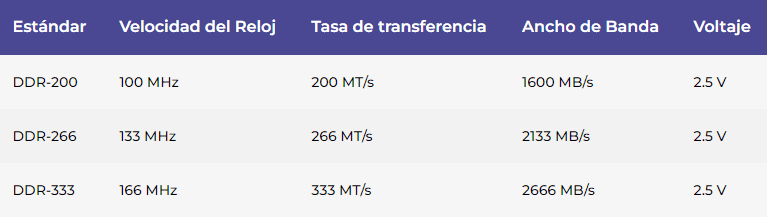

DDR1

DDR1 fue lanzado en el año 2000, sin embargo, no empezó a popularizarse hasta el 2002. Este tipo de memorias funcionaban con 2.6 V (2.5 en versiones anteriores), contaba con velocidades de reloj (bus) de hasta 200 MHz, un ancho de banda máximo de 3200 MB/s, y velocidades de transferencia de hasta 400 MT/s. Es necesario aclarar que todas estas especificaciones pertenecen al estándar DDR – 400.

Puede observar versiones anteriores del estándar en la siguiente imagen/tabla:

DDR1 SDRAM tuvo mejoras en el rendimiento que cambiarían el estándar en toda la industria. Seguidamente, DDR1 seria remplazado por la siguiente generación de memorias SDRAM (DDR2 SDRAM).

Nota: El buffer de precarga de las DDR1 soportaba únicamente 2 bits, es decir, dos palabras de datos por acceso a la memoria.

DDR2

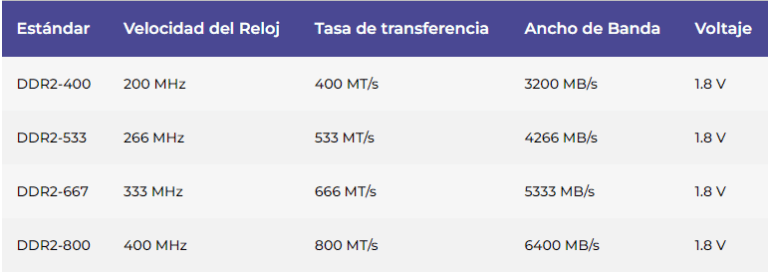

DDR2 fue lanzado en 2004, no obstante, fue vista por primera vez por parte de Samsung en 2001 (investigar), este tipo de memorias funcionaba con 1.8 V, contaba con velocidades de reloj (bus) de hasta 533 MHz, un ancho de banda máximo de 8500 MB/s, y velocidades de transferencia de hasta 1066 MT/s. Todas estas especificaciones pertenecen al estándar DDR2 – 1066.

Puede observar versiones anteriores del estándar en la siguiente imagen/tabla:

Nota: Las tablas no tiene el estándar para computadoras portátiles.

Esta nueva versión del estándar trajo consigo las siguientes características:

- Una reducción en el consumo energía en comparación con su predecesor (DDR1).

- Un aumento en el buffer de precarga de 4 bits por ciclo de reloj, este aumento permite un incremento en la velocidad del reloj, lo que a su vez proporciona un aumento en las MT/s.

- Un incremento en su ancho de banda, en la velocidad del reloj (bus) y la velocidades de transferencia.

DDR3

DDR3 fue lanzado en 2007, no obstante, Samsung presentaría el primer prototipo en 2005. Las memorias DDR3 funcionan con 1.5 V (1.35 en algunos estándares), cuenta con velocidades de reloj (bus) de hasta 1066 MHz, un ancho de banda máximo de 17066 MB/s, y velocidades de transferencia de hasta 2133 MT/s. Todas estas especificaciones pertenecen al estándar DDR3 – 2133.

Puede observar versiones anteriores del estándar en la siguiente imagen/tabla:

Esta nueva versión del estándar trajo consigo las siguientes características:

- Una reducción en el consumo energía en comparación con DDR2 (de 1.8 a 1.35 V).

- Un aumento en el buffer de precarga de 8 bits por ciclo de reloj, este aumento permite un incremento en la velocidad del reloj, lo que a su vez proporciona un aumento en las MT/s.

- Un incremento en su ancho de banda, en la velocidad del reloj (bus) y la velocidades de transferencia.

A pesar del lanzamiento de DDR4 en 2014, DDR3 aún sigue utilizándose hasta el día de hoy.

DDR4

DDR4 fue lanzado en 2014, remplazando a su antecesor DDR3. Las memorias DDR4 funcionan con 1.2 V (1.05 en algunos estándares), cuenta con velocidades de reloj (bus) de hasta 1600 MHz, un ancho de banda máximo de 25600 MB/s, y velocidades de transferencia de hasta 3200 MT/s. Todas estas especificaciones pertenecen al estándar DDR4 – 3200.

Puede observar versiones anteriores del estándar en la siguiente imagen/tabla:

Esta nueva versión del estándar trajo consigo las siguientes características:

- Una reducción en el consumo energía en comparación con DDR3 (de 1.35 a 1.05 V).

- Un incremento en su ancho de banda, en la velocidad del reloj (bus) y la velocidades de transferencia.

- En cuanto al buffer de precarga, este se mantuvo en 8 bits por ciclo de reloj.

DDR5

DDR5 fue lanzado en 2020, superando a su antecesor DDR4 en ciertos aspectos. Las memorias DDR5 funcionan con 1.1 V, cuenta con velocidades de reloj (bus) de hasta 3600 MHz, un ancho de banda máximo de 57600 MB/s, y velocidades de transferencia de hasta 7200 MT/s. Todas estas especificaciones pertenecen al estándar DDR5 – 7200.

Puede observar versiones anteriores del estándar en la siguiente imagen/tabla:

Esta nueva versión del estándar trajo consigo las siguientes características:

- Un incremento en el consumo energía en comparación con DDR4 (de 1.05 a 1.1 V).

- Un incremento descomunal en su ancho de banda, en la velocidad del reloj (bus) y la velocidades de transferencia.

- Aumento en el buffer de precarga de 16 bits por ciclo de reloj, este aumento permite un incremento en la velocidad del reloj, lo que a su vez proporciona un aumento en las MT/s.

- También se ha añadido una característica llamada Decisión Feedback Equalization (DFE) que permite un incremento en el ancho de banda y una mejora en el rendimiento.